| ID |

Date |

Author |

Type |

Category |

Subject |

|

119

|

12 Nov 2019 00:16 |

Yi Wang | Problem | Digitizer | V1725 error, runs keep crashing |

09:15:33.955 2019/11/12 [feov1725MTI00,ERROR] [feoV1725.cxx:663:link_thread,ERROR] Exiting thread 3 with error |

|

120

|

12 Nov 2019 00:23 |

Ben Smith | Problem | Digitizer | V1725 error, runs keep crashing |

It looks like there's a memory leak in the high voltage driver, and we were running out of memory (using a lot of swap). That *may* be related to the recent instability, but I'm not sure.

If things are more stable now, then the memory leak was probably the cause. If not, then we should try stopping the V1725 program, power-cycling the VME crate, then starting the V1725 program.

Yi: restarted the VME crate twice, now it seems like smooth. |

|

128

|

14 Nov 2019 00:09 |

Ben Smith | Problem | Hardware | Chronobox not serving human webpage |

The chronobox isn't serving the human-interactive webpage that should be visible at https://m-darkside.web.cern.ch/chronobox/ - it responds with "File not found". Oddly, it is still responding to API calls at /read_var, /write_var etc.

So shifters can still change between laser/noise/physics runs using the "Run type" page at https://m-darkside.web.cern.ch/?cmd=custom&page=Run%20type (which uses the API), but can't as easily monitor / sanity check the chronobox behaviour.

In the first instance, I think it would be useful to power-cycle the chronobox. If that doesn't work, I'm not sure how to proceed. |

|

1

|

11 Dec 2018 15:17 |

Thomas | Configuration | Software | Setup elog for ds-proto-daq |

1) Install and tweak elog:

[root@ds-proto-daq ~]# cat /etc/elogd.cfg

[global]

port = 8084

MTP host = trmail.triumf.ca

Use Email Subject = {$logbook} $Subject

Remove on reply = Author

Quote on reply = 1

URL = https://ds-proto-daq/elog/

[DS Prototype]

Theme = default

Comment = ELOG for DS Prototype MIDAS DAQ

Attributes = Author, Type, Category, Subject

Options Type = Routine, Problem, Problem Fixed, Configuration, Other

Options Category = General, Hardware, Digitizer, Trigger, MIDAS, Software, Other

Extendable Options = Category, Type

Required Attributes = Author, Type

Page Title = ELOG - $subject

Reverse sort = 1

Quick filter = Date, Type

Email all = lindner@triumf.ca

[root@ds-proto-daq ~]# systemctl start elogd.service

[root@ds-proto-daq ~]# systemctl is-active elogd.service

active

[root@ds-proto-daq ~]# systemctl enable elogd.service

2) Tweak apache and restart

[root@ds-proto-daq ~]# grep elog /etc/httpd/conf.d/ssl-ds-proto-daq.conf

ProxyPass /elog/ http://localhost:8084/ retry=1

[root@ds-proto-daq ~]# systemctl restart httpd

3) change MIDAS to use elog

[dsproto@ds-proto-daq bin]$ odbedit

[local:dsproto:R]/>cd Elog/

[local:dsproto:R]/Elog>create STRING URL

String length [32]: 256

[local:dsproto:R]/Elog>set URL https://ds-proto-daq.triumf.ca/elog/DS+Prototype/ |

|

2

|

11 Dec 2018 15:20 |

Thomas | Configuration | Software | Setup elog for ds-proto-daq |

1) Install and tweak elog:

[root@ds-proto-daq ~]# cat /etc/elogd.cfg

[global]

port = 8084

MTP host = trmail.triumf.ca

Use Email Subject = {$logbook} $Subject

Remove on reply = Author

Quote on reply = 1

URL = https://ds-proto-daq/elog/

[DS Prototype]

Theme = default

Comment = ELOG for DS Prototype MIDAS DAQ

Attributes = Author, Type, Category, Subject

Options Type = Routine, Problem, Problem Fixed, Configuration, Other

Options Category = General, Hardware, Digitizer, Trigger, MIDAS, Software, Other

Extendable Options = Category, Type

Required Attributes = Author, Type

Page Title = ELOG - $subject

Reverse sort = 1

Quick filter = Date, Type

Email all = lindner@triumf.ca

[root@ds-proto-daq ~]# systemctl start elogd.service

[root@ds-proto-daq ~]# systemctl is-active elogd.service

active

[root@ds-proto-daq ~]# systemctl enable elogd.service

2) Tweak apache and restart

[root@ds-proto-daq ~]# grep elog /etc/httpd/conf.d/ssl-ds-proto-daq.conf

ProxyPass /elog/ http://localhost:8084/ retry=1

[root@ds-proto-daq ~]# systemctl restart httpd

3) change MIDAS to use elog

[dsproto@ds-proto-daq bin]$ odbedit

[local:dsproto:R]/>cd Elog/

[local:dsproto:R]/Elog>create STRING URL

String length [32]: 256

[local:dsproto:R]/Elog>set URL https://ds-proto-daq.triumf.ca/elog/DS+Prototype/ |

|

9

|

31 Jan 2019 15:18 |

Pierre | Configuration | Trigger | Trigger rate |

Somehow the trigger rate was not matching the trigger source.

Find out that Link 3 was not collecting and possibly holding the fragment assembly in the main thread.

Swap Link3 <-> Link0 on the V1725, restarted.

Needs further investigation!

Date rate is fine now! CPU load is balanced on all 4 threads (~25%)

- irqbalance disabled

- change affinity for A3818 to cpu9: /etc/rc.local add: echo 0200 > /proc/irq/136/smp_affinity

Check : watch -n 0.1 'cat /proc/interrupts'

Maximum Trigger rate (HW buffer not rising) 1950 Evt/s => 200MB/s

for event size of 100KB composed of 4 banks with 32us per channel. |

|

10

|

06 Feb 2019 14:12 |

Pierre | Configuration | Hardware | Extended Trigger Time Tag (ETTT) |

Confirmed this ETTT configuration is working.

ETTT Enabled [22..21] = b10

|

v

Data [0x811C] = 0x 00 4 D 013C

ETTT Time [47..32]

| Ch Mask[16..0] Time[31..0]

| TTTTTT |

Header 1 v v v v

0xa0001914 0x00 0025 ff 0xff1ca598 0xe9c6e8a1 < event 1

0xa0001914 0x00 0025 ff 0xff1ca599 0xe9c82e25 < event 2

dTime : 0x25e9c82e25 − 0x25e9c6e8a1 = 0x14584 => 83332

Time interval: 8ns => 666.7e-6s => Freq: 1500Hz corresponding the current trigger rate

PAA |

|

14

|

19 Feb 2019 16:26 |

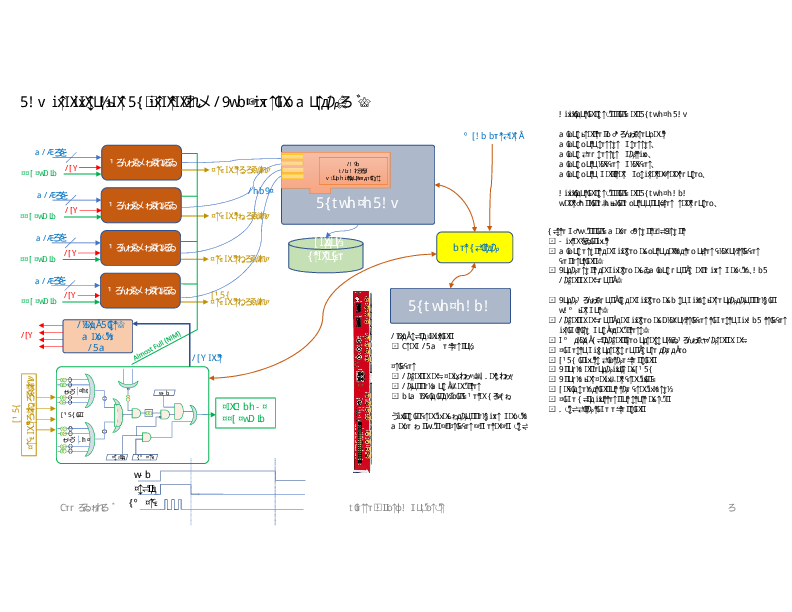

Pierre-A. | Configuration | General | Overall HW configuration |

For Reference,

I put a simple schematic for the Trigger/Run control.

Bryerton, please have a look. Let's try to issue 3..5 SW trigger before opening the HW trigger.

|

| Attachment 1: ds-proto-architecture-02.pdf

|

|

|

22

|

27 Mar 2019 08:57 |

Pierre | Configuration | Hardware | CERN setup |

Found that the Trigger out from the CB is on output1

Trigger / Not used

Clock / Not used

Set frontend to use NIM in/out instead of TTL as there is a nice

NIM-TTL-NIM adaptor CAEN Nim module available |

|

23

|

27 Mar 2019 14:04 |

Pierre | Configuration | Trigger | Time stamp sync |

The ChronoBox latest FW is loaded. Let tme know if this is what the chronobox should look like in term of registers.

Are we monitoring the PLL Lock Loss (odb: /DEAP Alarm ?)

Here is the dump of the 5 first sync triggers without any physics trigger behind.

1 0x830b577 0x17d7855 0x6b33d22 0x6b33d22 8.992791

2 0x830b577 0x17d7855 0x6b33d22 0x6b33d22 8.992791

3 0x830b577 0x17d7855 0x6b33d22 0x6b33d22 8.992791

4 0x830b577 0x17d7855 0x6b33d22 0x6b33d22 8.992791

1 0x830b581 0x2faf097 0x535c4ea 0x535c4ea 6.992792

2 0x830b581 0x2faf097 0x535c4ea 0x535c4ea 6.992792

3 0x830b581 0x2faf095 0x535c4ec 0x535c4ec 6.992792

4 0x830b581 0x2faf095 0x535c4ec 0x535c4ec 6.992792

1 0x830b587 0x47868d7 0x3b84cb0 0x3b84cb0 4.992792

2 0x830b587 0x47868d7 0x3b84cb0 0x3b84cb0 4.992792

3 0x830b587 0x47868d7 0x3b84cb0 0x3b84cb0 4.992792

4 0x830b587 0x47868d7 0x3b84cb0 0x3b84cb0 4.992792

1 0x830b5a1 0x5f5e119 0x23ad488 0x23ad488 2.992794

2 0x830b5a1 0x5f5e119 0x23ad488 0x23ad488 2.992794

3 0x830b5a1 0x5f5e117 0x23ad48a 0x23ad48a 2.992794

4 0x830b5a1 0x5f5e117 0x23ad48a 0x23ad48a 2.992794

1 0x830b5ab 0x7735959 0xbd5c52 0xbd5c52 0.992795

2 0x830b5ab 0x7735959 0xbd5c52 0xbd5c52 0.992795

3 0x830b5ab 0x7735959 0xbd5c52 0xbd5c52 0.992795

4 0x830b5ab 0x7735959 0xbd5c52 0xbd5c52 0.992795

With the physics triggers:

1 0x830b5c1 0x1834497f 0xeffc6c42 0x100393be 21.493591

2 0x830b5c1 0x1834497f 0xeffc6c42 0x100393be 21.493591

3 0x830b5c1 0x1834497f 0xeffc6c42 0x100393be 21.493591

4 0x830b5c1 0x1834497f 0xeffc6c42 0x100393be 21.493591

1 0x830b5d3 0x1834abb5 0xeffc0a1e 0x1003f5e2 21.495601

2 0x830b5d3 0x1834abb5 0xeffc0a1e 0x1003f5e2 21.495601

3 0x830b5d3 0x1834abb5 0xeffc0a1e 0x1003f5e2 21.495601

4 0x830b5d3 0x1834abb5 0xeffc0a1e 0x1003f5e2 21.495601

1 0x830b5dd 0x18350d7f 0xeffba85e 0x100457a2 21.497603

2 0x830b5dd 0x18350d7f 0xeffba85e 0x100457a2 21.497603

3 0x830b5dd 0x18350d7f 0xeffba85e 0x100457a2 21.497603

4 0x830b5dd 0x18350d7f 0xeffba85e 0x100457a2 21.497603

1 0x830b5e3 0x183585e7 0xeffb2ffc 0x1004d004 21.500068

2 0x830b5e3 0x183585e7 0xeffb2ffc 0x1004d004 21.500068

3 0x830b5e3 0x183585e7 0xeffb2ffc 0x1004d004 21.500068

4 0x830b5e3 0x183585e7 0xeffb2ffc 0x1004d004 21.500068

1 0x830b5ed 0x1a10bb9b 0xee1ffa52 0x11e005ae 23.991535

2 0x830b5ed 0x1a10bb9b 0xee1ffa52 0x11e005ae 23.991535

3 0x830b5ed 0x1a10bb9b 0xee1ffa52 0x11e005ae 23.991535

4 0x830b5ed 0x1a10bb9b 0xee1ffa52 0x11e005ae 23.991535

1 0x830b5fb 0x1a111f65 0xee1f9696 0x11e0696a 23.993578

2 0x830b5fb 0x1a111f65 0xee1f9696 0x11e0696a 23.993578

3 0x830b5fb 0x1a111f65 0xee1f9696 0x11e0696a 23.993578

4 0x830b5fb 0x1a111f65 0xee1f9696 0x11e0696a 23.993578

1 0x830b607 0x1a118115 0xee1f34f2 0x11e0cb0e 23.995577

2 0x830b607 0x1a118115 0xee1f34f2 0x11e0cb0e 23.995577

3 0x830b607 0x1a118115 0xee1f34f2 0x11e0cb0e 23.995577

4 0x830b607 0x1a118115 0xee1f34f2 0x11e0cb0e 23.995577

1 0x830b611 0x1a11e2c7 0xee1ed34a 0x11e12cb6 23.997577

2 0x830b611 0x1a11e2c7 0xee1ed34a 0x11e12cb6 23.997577

3 0x830b611 0x1a11e2c7 0xee1ed34a 0x11e12cb6 23.997577

4 0x830b611 0x1a11e2c7 0xee1ed34a 0x11e12cb6 23.997577

The ZMQ0 banks:

#banks:5 Bank list:-ZMQ0W200W201W202W203-

Bank:ZMQ0 Length: 40(I*1)/10(I*4)/10(Type) Type:Unsigned Integer*4

1-> 0x000a5f1c 0x000000c4 0x00000001 0x0ebd5273 0x00000001 0x00010001 0xffffffff 0x00000000

9-> 0xffff0000 0x00000000

------------------------ Event# 10 ------------------------

#banks:5 Bank list:-ZMQ0W200W201W202W203-

Bank:ZMQ0 Length: 40(I*1)/10(I*4)/10(Type) Type:Unsigned Integer*4

1-> 0x000a5f1d 0x000000c5 0x00000001 0x0ebd5279 0x00000001 0x00010001 0xffffffff 0x00000000

9-> 0xffff0000 0x00000000

[dsproto@ds-proto-daq dsproto_daq]$ |

|

24

|

28 Mar 2019 02:18 |

Pierre | Configuration | Trigger | Test |

|

|

32

|

12 Jul 2019 01:27 |

Marco Rescigno | Configuration | | MB1 test in proto-0 setup/1 |

Changed custom size to 500 (20 us), tested ok run 681 |

|

47

|

27 Oct 2019 06:08 |

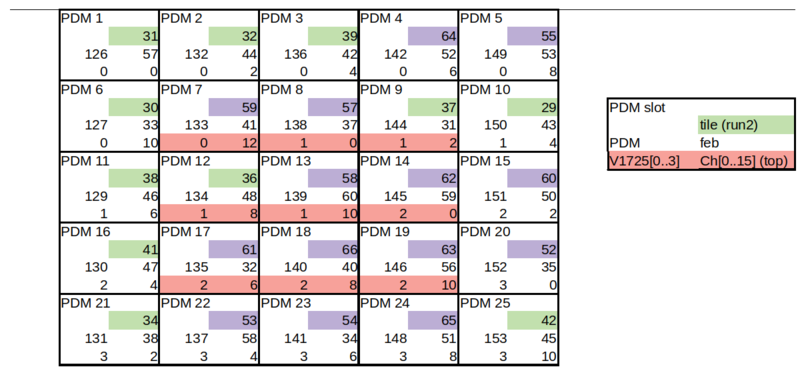

Simone Stracka | Configuration | Hardware | Converters installed in VME crate |

People: Edgar, Simone

Installed differential to single-ended converters in VME crate, and turned crate back on. elog:47/2

Channel count in the converters is 0 to 15 starting from the low end. Wired according to:

left board, channels 0..15 = PDM slot 1..16

right board, channels 0..8 = PDM slot 17..25

N.B. V1725 board #0 logic level is set to TTL (boards #1, #2, #3 to NIM) elog:47/3

In ODB / Equipment / V1725_Data00 / Settings / set Channel Mask to 0x1555 for all V1725 boards (enables channels 0 2 4 6 8 10 12)

(board 0 receives 7 PDM inputs, boards 1,2,3 receive 6 PDM each)

In https://ds-proto-daq.cern.ch/chronobox/ , set Enable Channel [ch_enable] = 0x3F3F3F7F , Channel Assignment [ch_assign] = 0x00393340.

9 central PDM's assigned to "top" group, external PDM's assigned to "bottom" group elog:47/1

Wiki instructions with the script to get the CDM back into a sensible state seem outdated. The variables seem fine, though ...

[dsproto@ds-proto-daq ~]$ esper-tool read 192.168.1.5 cdm ext_clk

[49999632]

[dsproto@ds-proto-daq ~]$ esper-tool read 192.168.1.5 lmk pll1_ld

[1]

[dsproto@ds-proto-daq ~]$ esper-tool read 192.168.1.5 lmk pll2_ld

[1]

|

| Attachment 1: PDMadcCh.png

|

|

| Attachment 2: converters.jpg

|

|

| Attachment 3: adc0_ttl.jpg

|

|

|

52

|

28 Oct 2019 15:10 |

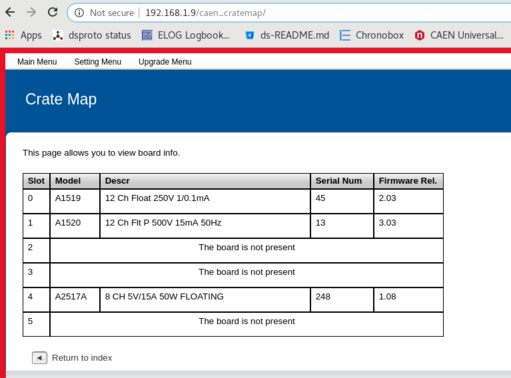

Simone Stracka | Configuration | Hardware | LV for steering module and current status of CAEN mainframe |

The HV board from Naples did not turn on: Yury gave it to the CAEN guys to check and/or bring back for replacement.

Yi and Luigi rented a new HV module (A1519). The HV module (A1520P) we used for tests of the I-V script is also present in the Mainframe (see below).

The first 24 channels (slots 0 and 1) are therefore HV. If the new HV does not show up on time we'll try and adapt the cables to work with A1519.

The A2517A module is LV. This is currently operated from the DAQ pc using CAEN_HVPSS_ChannelsController.jnlp (located in the Desktop/SteeringModule folder).

The three low voltage channels (0,1,2) should be turned on at the same time by setting Pw = ON.

Settings:

Channel 0 and 1: I0Set = 2.0 A , V0Set = 2.5 V , UNVThr = 0 V, OVVThr = 3.0 V, Intck = Disabled

IMon = 1.44 (this depends on the illumination) , VMon = 2.48 V , VCon = 2.79 V

Channel 2: I0Set = 1.0 A , V0Set = 5.0 V , UNVThr = 0 V, OVVThr = 5.5 V, Intck = Disabled

IMon = 0.07 , VMon = 4.998 V , VCon = 5.02 V

In case the channels trip they cannot be ramped back up unless the alarms are cleared.

|

| Attachment 1: CAENmainframe.png

|

|

|

55

|

01 Nov 2019 06:50 |

Alex Kish | Configuration | Hardware | Turn off the fields |

Ramp down the fields, in 200V steps.

Nominal values:

1st ring: 4180 V

wire gate: 3780 V

cathode: 6180 V |

|

58

|

01 Nov 2019 09:49 |

Alex Kish | Configuration | Hardware | Turn off the fields |

Ramp UP the fields, in 100V steps.

Nominal values:

1st ring: 4180 V

wire gate: 3780 V

cathode: 6180 V |

|

65

|

04 Nov 2019 06:02 |

Alex Kish | Configuration | Hardware | Increased fields! |

Increased drift and extraction fields.

Current settings: wire gate 5100 V, 1st ring: 6100 V, cathode: 11100 V

P.S. Increased by in the morning by Yi. |

|

66

|

04 Nov 2019 07:57 |

Ben Smith | Configuration | Software | Package installations |

This morning I installed the xrootd-client and python3-devel packages from yum. For the latter to work, I needed to do a yum update. This was long overdue, and updated 1200+ packages.

I have compiled a new version of ROOT 6 that links to Python 3. This will allow us to use ROOT and midas from the same python scripts. |

|

67

|

04 Nov 2019 08:00 |

Ben Smith | Configuration | MIDAS | Change of location of history files |

/home was getting very full on ds-proto-daq, so I moved the history files onto the /data disk. There is now a symlink from ~/online/history to /data/dsproto/history/. |

|

70

|

05 Nov 2019 01:22 |

Ben Smith | Configuration | Digitizer | V1725 board config |

The V1725s have been changed to have board config 0x50 rather than 0x10. This means that they will now trigger on the leading edge of the pulse rather than the tailing edge. There is now much less jitter in the location of pulses in the digitized waveforms. |