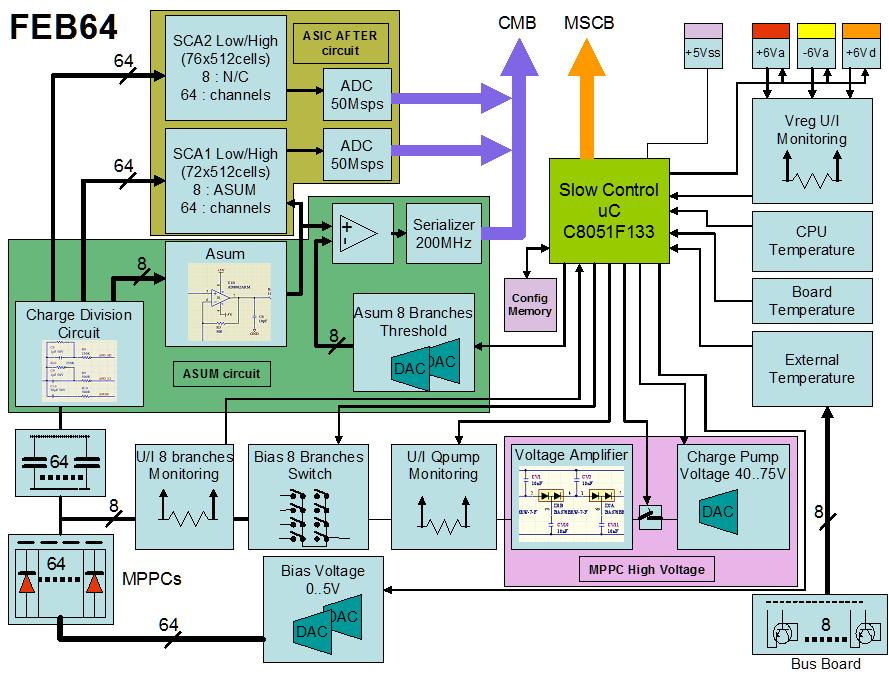

FrontEnd Board 64 (FEB64)

1

Purpose

The FEB64 board handles 64 MPPC Silicon PM mounted in the FGD detector. Its main purpose is to read the 64 (76) MPPC channels. The information is stored in the AFTER SCA chip (Analog memory). For every trigger, each cell of the analog memory (76x512 cells) is digitized, the digital value representing the amplitude at a given time (20Msps) is transmitted to the CMB card. In parallel to its main function, the FE64 has a "slow control" section which run completely independently from the data acquisition section and provides card condition status, board and internal detector temperature monitoring and control/monitoring of the high voltage fed to the MPPCs.

Functions

- S/N Card : Card Serial Number.

- FEB64 board condition monitoring : Board condition monitoring.

- Vreg U/I Monitoring : Voltages and Currents monitoring.

- Board Temperature monitoring : Board and micro controller temperature monitoring.

- External Temperature (SST) : FGD Internal detector temperature monitoring.

- MPPC High Voltage : High Voltage control for each MPPC.

- Charge Pump Voltage : Charge pump voltage setting.

- U/I QPump Monitoring : Charge pump voltage and current.

- Bias 8 Branches Switch : Each of 8 switches is associated with 8 consecutive MPPC.

- U/I 8 Branches Monitoring : Voltage and current associated to each of the 8 MPPC branches.

- Bias Voltage 0..5V : MPPC 64 DAQs

- ASIC AFTER circuit : MPPC signal processing.

- ASUM circuit : Analog sum signal for trigger generation (transmitted to CMB card).

- Config Memory : Permanent configuration parameter saving/restoring.

- The MSCB user_data_type contains all the communication variables to the FEB64 card.

Operation

- By default at power up the main elements of the card are kept unpowered.

- By default configuration from the EEPROM page 0 of the onboard memory is restored.

- To power up the card:

- CTL register(idx:2) Set bit ^ 0 [0x1]

- CSR register(idx:3) will show bit ^ 0 = 1/0 (1=on, 0=off)

- To power down the card:

- CTL register(idx:2) Set bit ^ 7 [0x80] Manual Shutdown

- CSR register(idx:3) will show bit ^ 0 = 1/0 (1=on, 0=off)

- To power up the Charge pump:

- The Charge Punmp is by default turned ON during the Card power up.

- The CSR register will show bit ^ 1 = 1/0 (1=on, 0=off)

Location

This card is located in each "crate" mounted on the surrounding structure of each FGD (24 crates per FGD). Each crate contains 4 FEB64 cards.

1.6.1

1.6.1